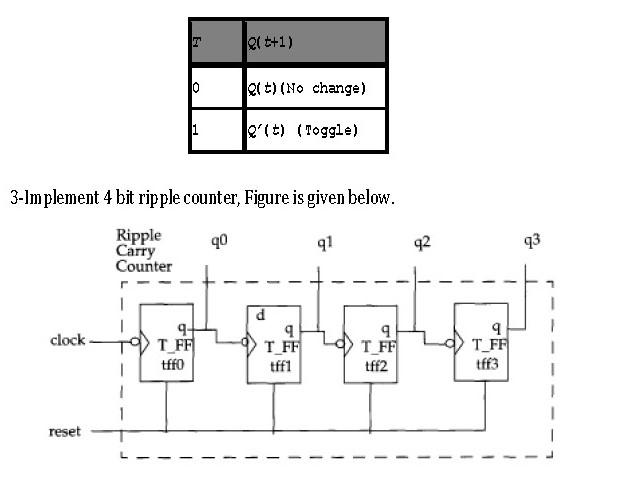

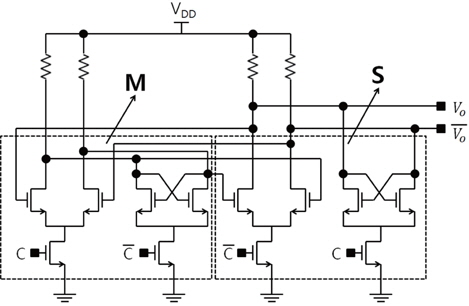

A CML latch consisting of a differential pair and a regenerative pair. | Download Scientific Diagram

Sensors | Free Full-Text | Design of Dual-Mode Local Oscillators Using CMOS Technology for Motion Detection Sensors

A Ku-band dual control path frequency synthesizer using varactorless Q-enhanced LC-type VCO | SpringerLink

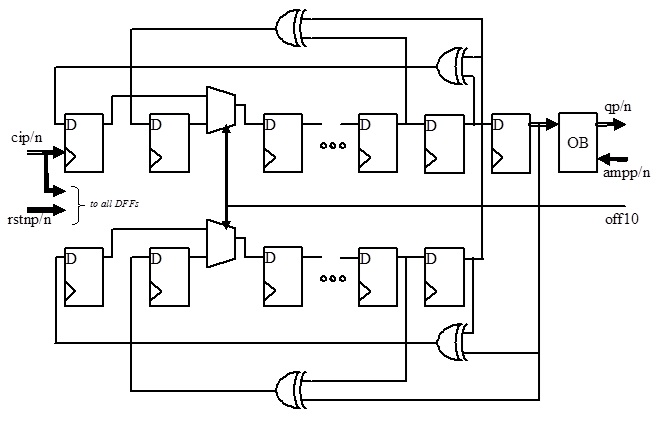

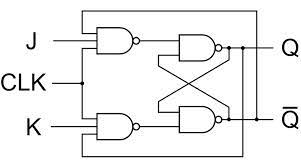

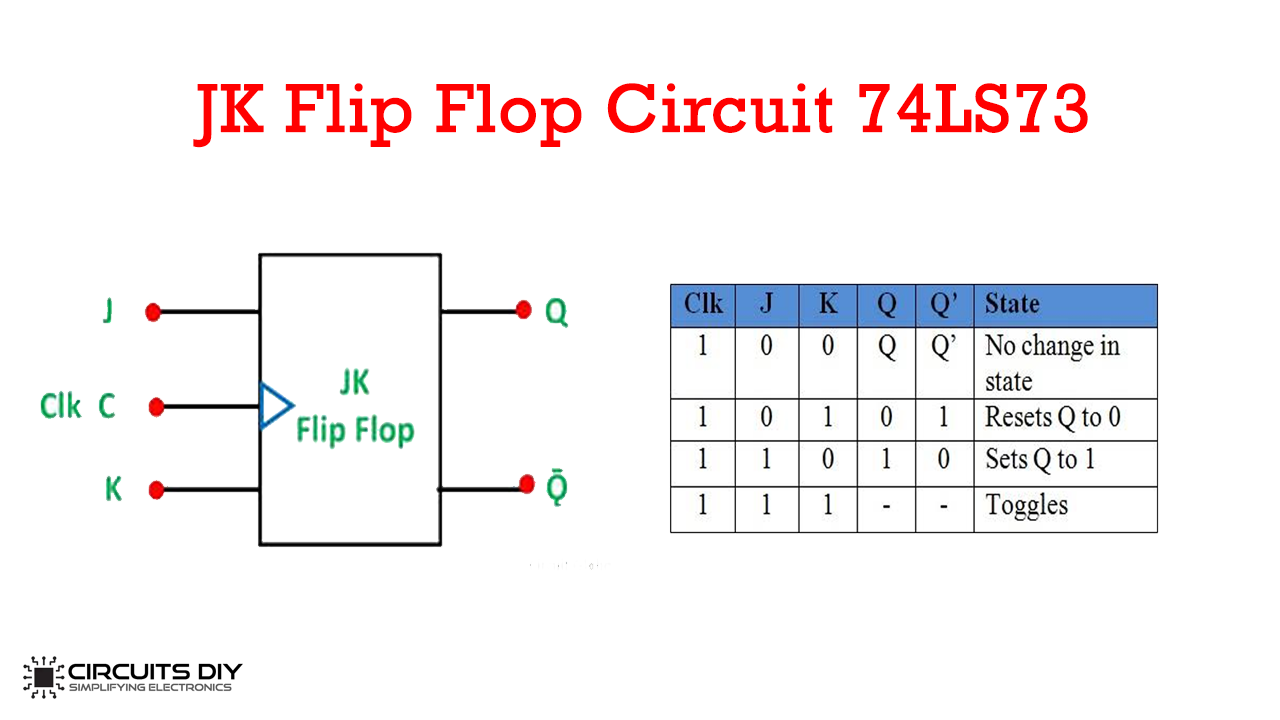

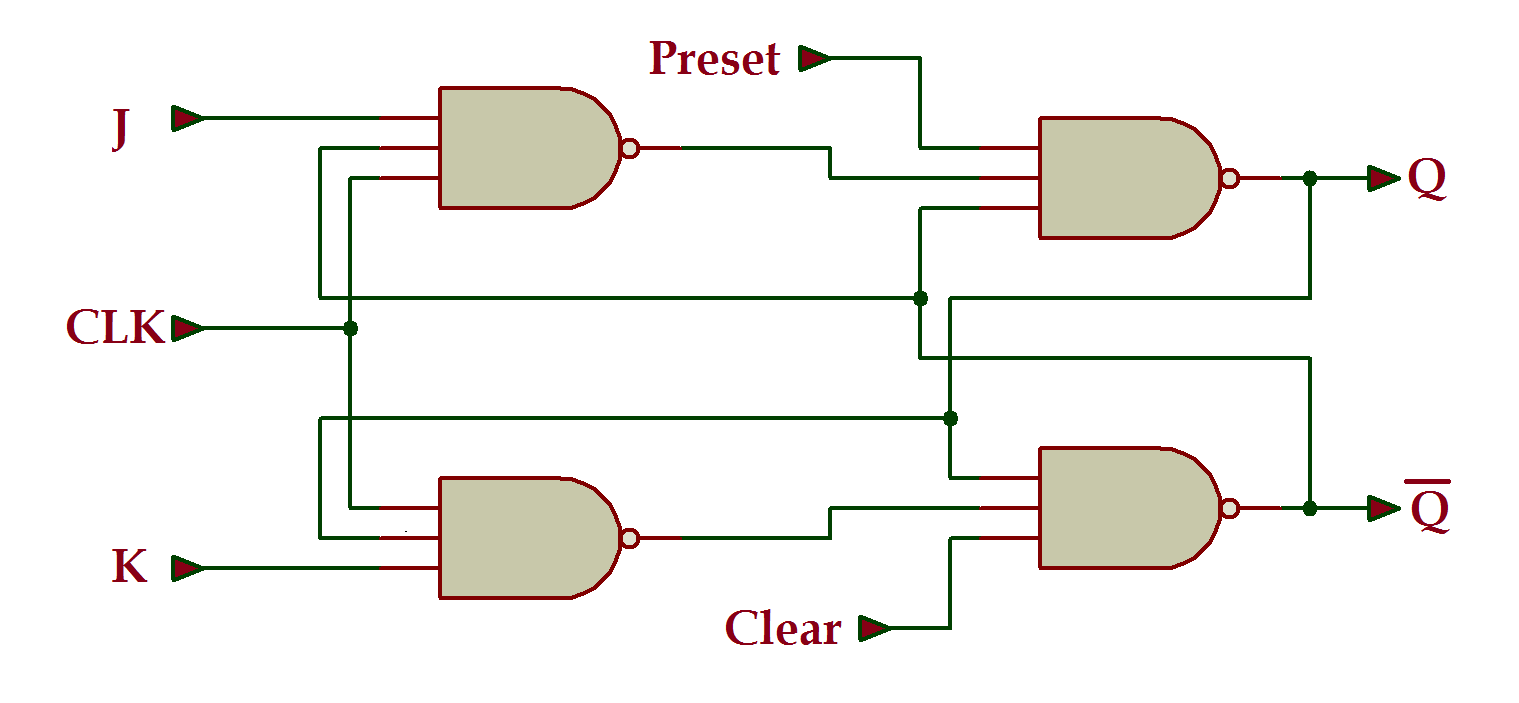

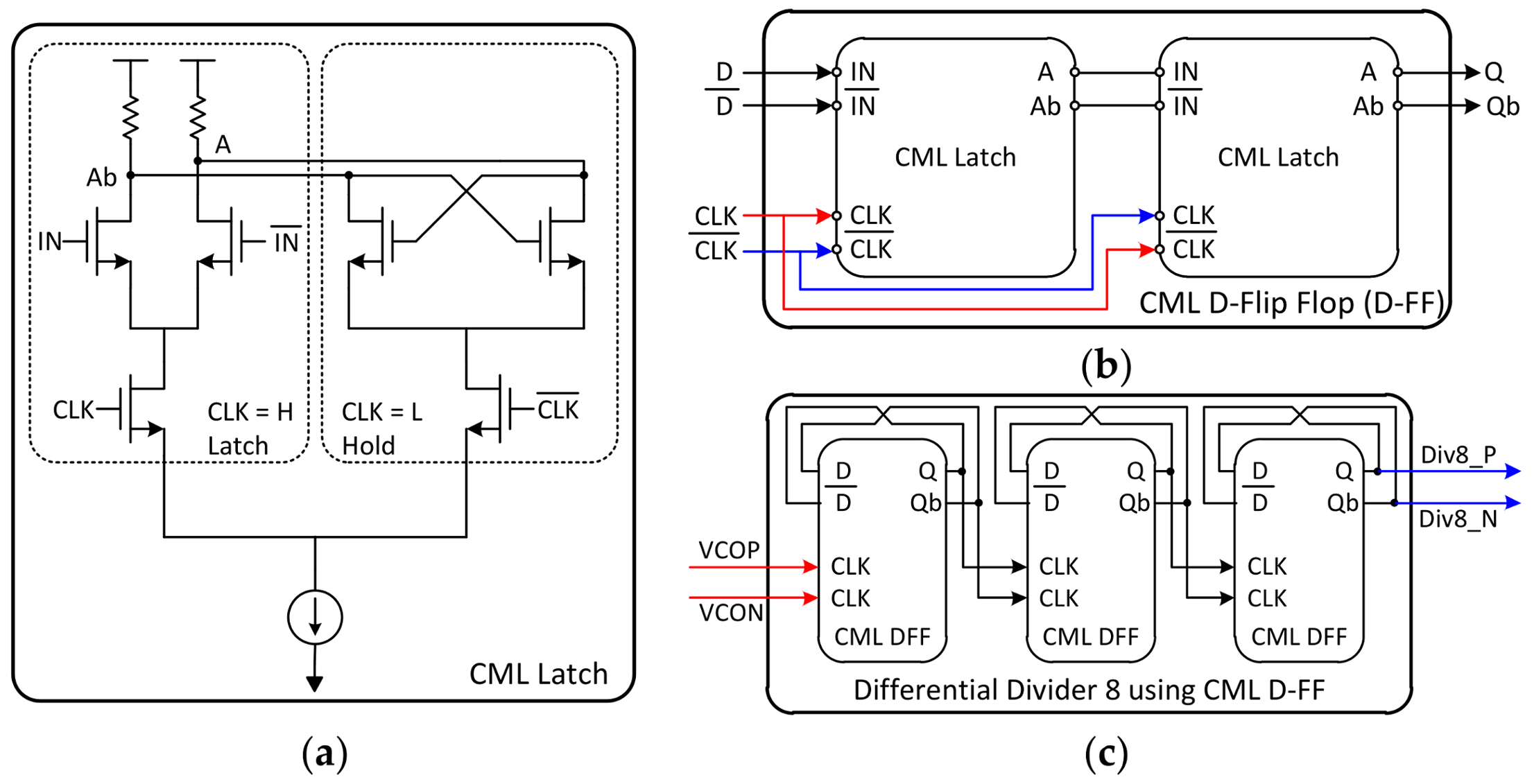

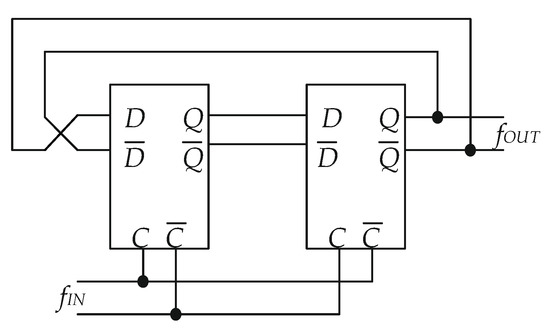

Electronics | Free Full-Text | A Power Efficient Frequency Divider With 55 GHz Self-Oscillating Frequency in SiGe BiCMOS

OAK 국가리포지터리 - OA 학술지 - Transactions on Electrical and Electronic Materials - High-speed CMOS Frequency Divider with Inductive Peaking Technique

A Compact Inductorless 32 GHz Divide-by-2 CML Frequency Divider on 22 nm FD-SOI Technology | Semantic Scholar

Energy Efficient High-Speed Links Electrical and Optical Interconnect Architectures to Enable Tera-Scale Computing